- 您现在的位置:买卖IC网 > Sheet目录3862 > PIC18F26J13-I/SS (Microchip Technology)IC PIC MCU 64KB FLASH 28SSOP

2010-2012 Microchip Technology Inc.

DS41412F-page 65

PIC18(L)F2X/4XK22

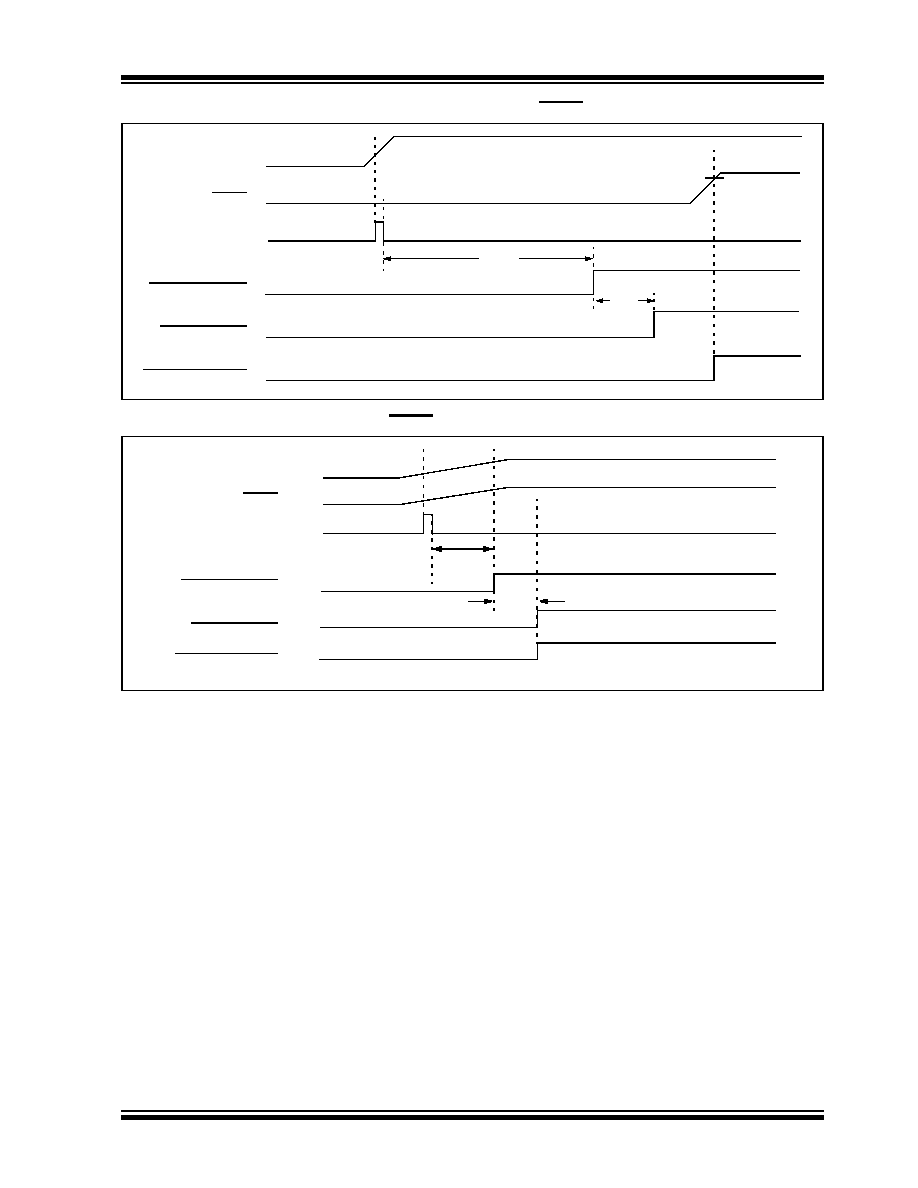

FIGURE 4-5:

TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

FIGURE 4-6:

SLOW RISE TIME (MCLR TIED TO VDD, VDD RISE > TPWRT)

VDD

MCLR

INTERNAL POR

PWRT TIME-OUT

OST TIME-OUT

INTERNAL RESET

TPWRT

TOST

VDD

MCLR

INTERNAL POR

PWRT TIME-OUT

OST TIME-OUT

INTERNAL RESET

0V

5V

TPWRT

TOST

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

SFW27R-1STE1

SFW27R-1STE1-FFC/FPC CONN

PIC18F66J15-I/PT

IC PIC MCU FLASH 48KX16 64TQFP

PIC24FV32KA302-I/SO

MCU 32KB FLASH 2KB RAM 28-SOIC

PIC24HJ64GP204-I/ML

IC PIC MCU FLASH 64K 44-QFN

SFW27R-2STE1

SFW27R-2STE1-FFC/FPC CONN

PIC24F16KA302-I/SP

MCU 16KB FLASH 2KB RAM 28-SPDIP

PIC18LF45J11-I/ML

IC PIC MCU FLASH 32K 2V 44-QFN

PIC24F32KA302-I/SO

MCU 32KB FLASH 2KB RAM 28-SOIC

相关代理商/技术参数

PIC18F26J13T-I/ML

功能描述:8位微控制器 -MCU GP 64KB 4KB RAM 12 MIPS 12b ADC nanoWat RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F26J13T-I/SO

功能描述:8位微控制器 -MCU GP 64KB 4KB RAM 12 MIPS 12b ADC nanoWat RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F26J13T-I/SS

功能描述:8位微控制器 -MCU GP 64KB 4KB RAM 12 MIPS 12b ADC nanoWat RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F26J50-EVK

制造商:Embest Info&Tech Co Ltd 功能描述:PIC18F26J50 FLOWCODE 4 DEV KIT 制造商:Microchip Technology Inc 功能描述:PIC18F26J50, FLOWCODE 4, DEV KIT 制造商:Microchip Technology Inc 功能描述:PIC18F26J50, FLOWCODE 4, TEMP SENSOR, DEV KIT; Silicon Manufacturer:Microchip; Core Architecture:PIC; Core Sub-Architecture:PIC18; Silicon Core Number:PIC18F; Silicon Family Name:PIC18FxxJxx ;RoHS Compliant: Yes

PIC18F26J50-I/ML

功能描述:8位微控制器 -MCU Full Spd USB 64KB Flsh 4KBRAM nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F26J50-I/SO

功能描述:8位微控制器 -MCU Full Spd USB 64KB Flsh 4KBRAM nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F26J50-I/SP

功能描述:8位微控制器 -MCU Full Spd USB 64KB Flsh 4KBRAM nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F26J50-I/SS

功能描述:8位微控制器 -MCU Full Spd USB 64KB Flsh 4KBRAM nanoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT